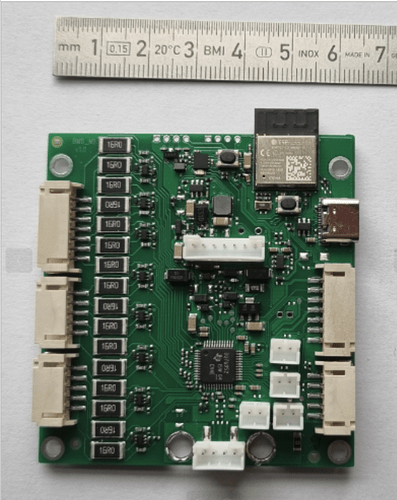

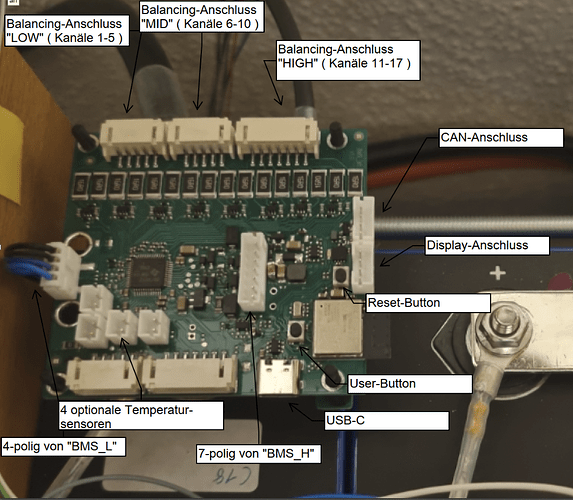

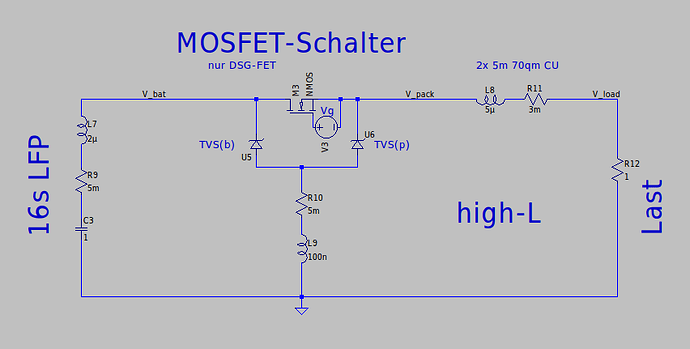

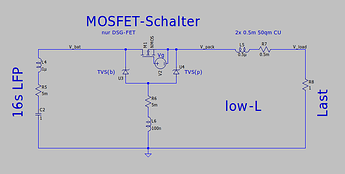

Es gibt einige Updates zum MOSFET-Schalter meines BMS:

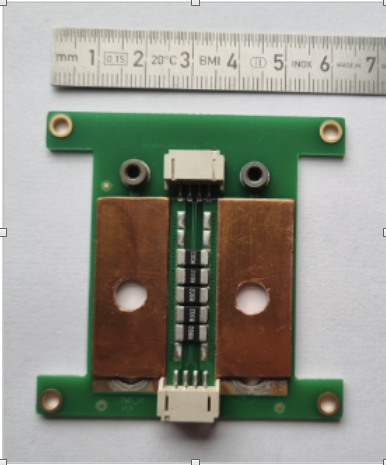

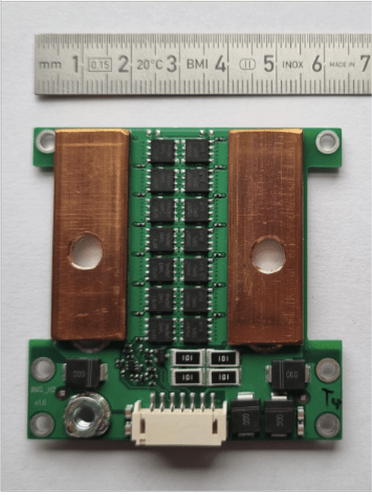

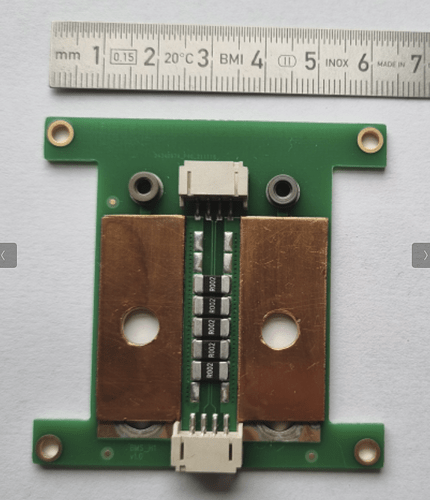

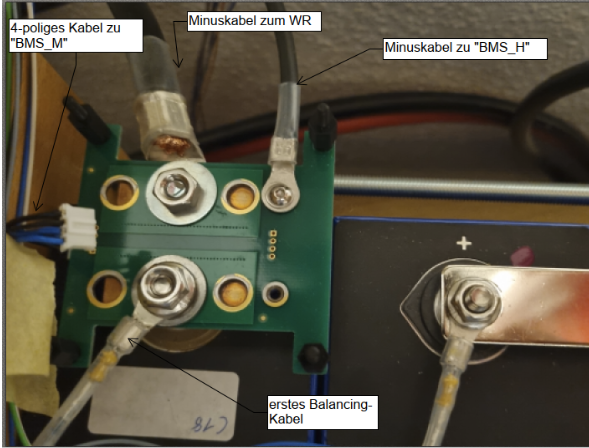

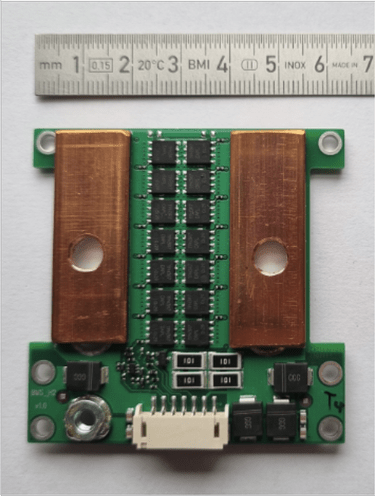

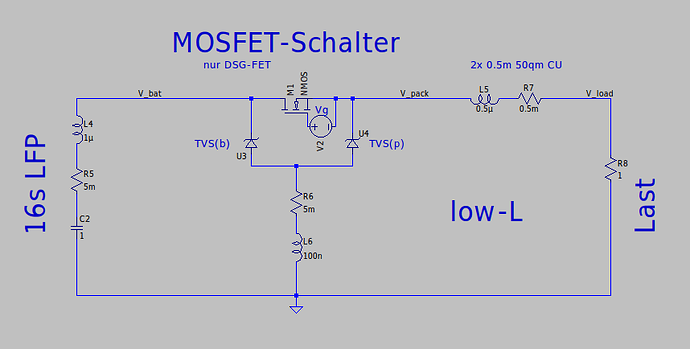

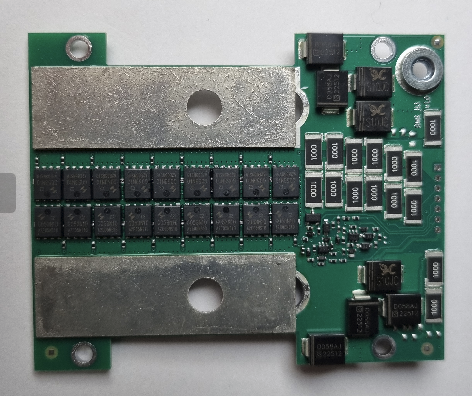

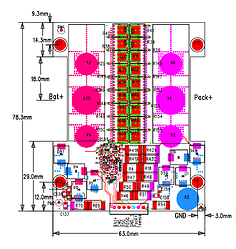

Von der Variante für die Montage direkt auf den 280Ah-Zellen habe ich Muster des MOSFET-Schalters mit optimiertem Abschalt-Timing bestückt:

Meine elektronische Pulslast hat ein HW-Update bekommen und kann nun bei bis zu 60 V Strompulse bis ~ 1200 A erzeugen, also eine Pulsleistung von > 70 kW.

Damit habe ich in den letzten Tagen den optimierten MOSFET-Schalter getestet.

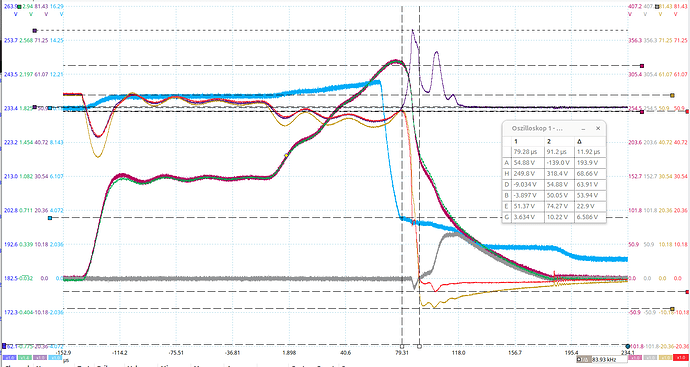

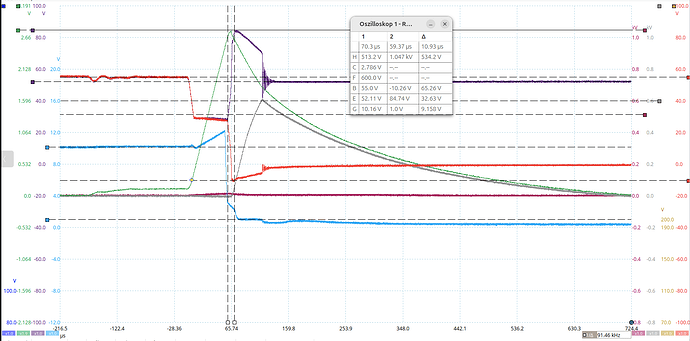

Das folgende Bild ist mit einem 18p bestückten MOSFET-Schalter entstanden.

Die Abschaltschwelle war dabei im BMS auf ~ 512 A konfiguriert, also ein Wert wie man ihn für ein BMS der 150 A - 200 A Klasse verwenden würde.

Die batterieseitige und lastseitige Induktivität war dabei jeweils ~ 1.5 uH. ( Tests mit mehr Induktivität werden noch folgen )

Es wurde mit einer Batteriemulation aus 48 low-ESR Elkos gearbeitet.

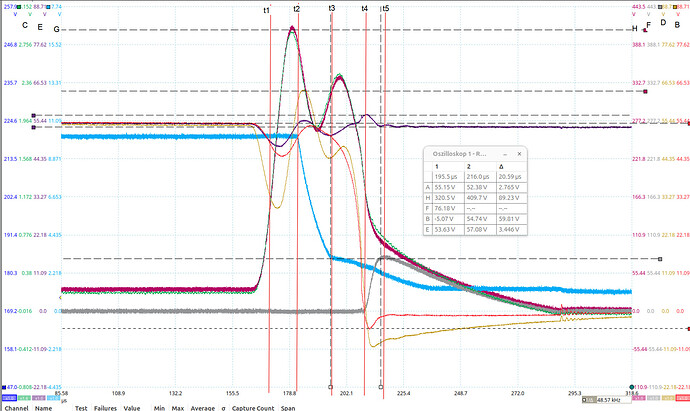

Die Kurve C (grün) ist der Strom im Lastkreis, also durch L5 bzw. R7

Das Oszi zeigt hier die 20fach verstärkte Spannung über einen ~135 uOhm Shunt.

Die Messung wurde bei geringeren Strömen mit einer Stromzange, die bei ~ 700 A in Sättigung geht, kalibriert und kann auch über die Skala von H (pink) 1 V = 1 A abgelesen werden.

Die Kurve F (grau) ist der Strom durch R6 bzw. L6 ( also der kombinierte Ableitstrom der (Überspannung-)Schutzdioden U3 und U4. 1V <=> 1 A

Die Kurve G (hellblau) ist die Gate-Source-Spannung (Vg) der Discharge-FETs M1

Die Kurve E (lila) ist die Batteriespannung (V_bat).

Die Kurve B (rot) ist die Ausgangsspannung des BMS (V_pack).

(hier zum besseren Verständnis der Beschreibung erneut eingefügt: )

Der Lastseitige Strom steigt in ~ 70 us von ~ 40 A auf ~ 1050 A. Die Spannung am BMS ( Kurve E (lila) und Kurve B (rot) ) bricht dabei wegen der batterieseitigen Induktivität um ~ 26 V ein

Vom Erreichen der Stromabschaltschwelle ( ~ 512 A ) dauert es ~ 25 us bis die Entladung des Gates der Discharge-FETs M1 beginnt.

Bis zum Erreichen des Miller-Plateaus der FETs dauert es < 5 us. Im Anschluss beginnen die FETs zu sperren.

Der Bereich, in dem die FETs von leitend zu sperrend wechseln, ist mit den Zeit-Markern abgegrenzt und dauert ~ 10 us

Wegen der Induktivitäten kann der Strom im Batterie- und Lastkreis nicht so abrupt stoppen.

Dies erkennt man daran, dass

a) die batterieseitige Spannung, Kurve E (lila), nur durch U5 begrenzt kurzzeitig auf fast 85 V hochschnellt. Dadurch klingt der Stromfluss im Batteriekreis in ~ 50 us ab.

b) die lastseitige Spannung fällt auf bis zu ~ - 10 V da der Strom nun durch U6 getragen wird. Wegen der viel geringeren Spannung dauert es ~ 600 us bis der lastseitige Strom abgeklungen ist.

c) Die durch die unterschiedliche Abklingrate zunehmende Differenz der Ströme durch U5 und U6 sieht man in Kurve F (grau)

Wegen leichtem Skalierungsfehler und beginnender Sättigung der Stromzange treffen sich Kurve C (grün) und Kurve F (grau) nicht wie eigentlich erwartet an einem Punkt um dann deckungsgleich abzuklingen, sondern konvergieren nur langsam.

Die Optimierungen zur älteren HW-Revision sind abgesehen von den nun viel höheren Testströmen ( ~1000 A vs ~320 A ) subtil aber wichtig.

Die Zeitspanne für die die Gatespannung, Kurve G (hellblau), im Übergangsbereich ( <= 10 V, >= 1 V ) liegt, hat sich von etwa 40 us auf 20 us halbiert und sieht nun genauso aus, wie ich sie haben wollte.

Das Sperren der FETs wird dadurch "härter" und minimiert die Belastung der FETs. Mit der älteren HW-Revision hätten die FETs wegen suboptimalem Verlauf der Gatespannung bei so hohen Strömen viel länger noch einen Teil des Stroms getragen und damit die FETs unnötig belastet.

Von solchen Abschalttests habe ich nicht nur einige wenige, sondern > 1000 durchgeführt.

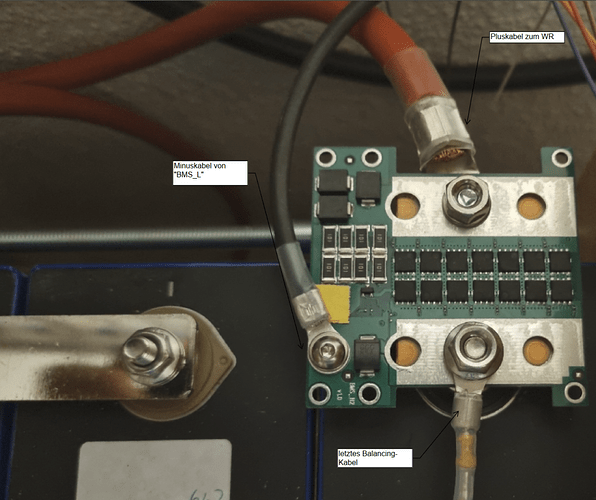

Mit diesem Verhalten bin ich nun sehr zufrieden und werde mit dieser Dimensionierung in den nächsten Wochen nun die Variante mit integriertem Shunt und bis zu 24p FETs zur abgesetzten Montage bestücken und testen.