Bei einem Sperrwandler ( Flyback ) wird die gesamte transportierte Energie induktiv im "Transformator" zwischengespeichert. ( Was das betrifft die worst-case Topologie )

Bei den hier von mir erwähnten Full-Bridge (FB) Topologien ist das natürlich nicht der Fall.

Idealisiert wird hier garnichts induktiv im Transformator gespeichert. Real hat man natürlich die Magnetisierungsinduktivität und bei LLC oder CLLC auch noch zusätzliche "serielle" Induktivitäten, um die resonanten Schaltvorgänge zu ermöglichen .

Bei Leistungsdichte und auch möglicher Effizienz hat ein Flyback auch deswegen systematische Nachteile gegenüber den FB Varianten.

Bei den aktuellen GAN QR-Flybacks für Handy- und kleine Laptop-Netzteile schafft man vielleicht die 95 % Wirkungsgrad.

Bei LLC/ CLLC ( 400 V <=> 50 V ) sind 98% keute kein Kunststück mehr und 99% möglich.

Deswegen findet man Flybacks auch eher bei < 100 W und praktisch nie im kW Bereich.

Bzgl. der Skalierung von magnetischen Bauteilen ist es aber bei all diesen Topologien so, dass sich mit einer Verdopplung der Frequenz das Bauteilvolumen idealisiert halbiert.

Bei einer "reinen" Induktivität ist es die Nenninduktivität die halbiert werden kann.

Bei einem "reinen" Transformator halbiert sich das Vt-Produkt so dass für die gleiche maximale Flussdichte nur der halbe magnetische Querschnitt benötigt wird, anders ausgedrückt braucht man weniger Magnetisierungsinduktivität.

Dies ist das Grundprinzip der Evolution der Leistungselektronik der letzten ~40 Jahre, die im Grunde mit den ersten Leistungs-MOSFETs richtig begonnen hat.

Hallo,

ich habe jetzt einen Einzelzellentest zur Effizienz durchgeführt. Gnutzt habe ich den EBC-A20.

In den vollständig entladenen Akku (Entladen auf 1,5 Volt nach Herstellerangabe, dann eine Stunde ruhen lassen. Die Spannung pendelt sich dann bei 1,8 V ein.) konnte ich 214,1 Ah und 656,8 Wh Energie pumpen. Die Ladeschlussspannung liegt bei 3,95 V.

Nach dem Laden ebenfalls eine Stunde ruhen gelassen und dann wieder bis 1,5 V entladen. Dabei konnte ich 214,2 Ah und 636,5 Wh entnehmen.

Damit erreichen diese Zellen einen Wirkungsgrad von 96,9%. Aufgrund der Erfahrungen anderer Nutzer hier im Forum und Untersuchungen zum Beispiel der HTW hatte ich einen niedrigeren Wert erwartet. Scheinbar ist auch hier die Entwicklung weiter gegangen.

Das ist zunächst der Wirkungsgrad der Einzelzelle. Wie der Wirkungsgrad des Gesamtsystems dann aussieht, bleibt abzuwarten. Aber das hier ist auf jeden Fall ein guter Ausgangswert.

Grüße

Thomas

Auf was hattst du laden und entladen eingestellt?

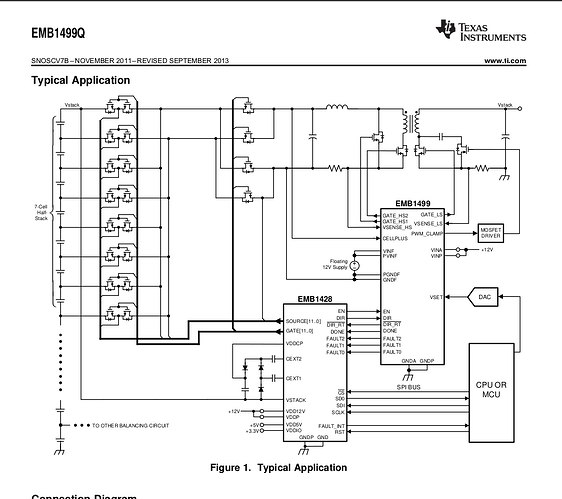

Für einen Hochvolt-Speicher dürfte ein Balancer zwischen den 14/16s Stapeln doch so auch funktionieren?

Vielen Dank für die Messung.

Das klingt doch ziemlich ermutigend.

Gehe ich richtig in der Annahme, dass du mit den vollen 20 A (ent)-laden hast?

Hast Du das beim EBC-A20 mitgelieferte Kabel mit Kroko-Klemmen zum Anschluss der Zelle verwendet oder ein eigenes mit Gabelschuhen hergestellt?

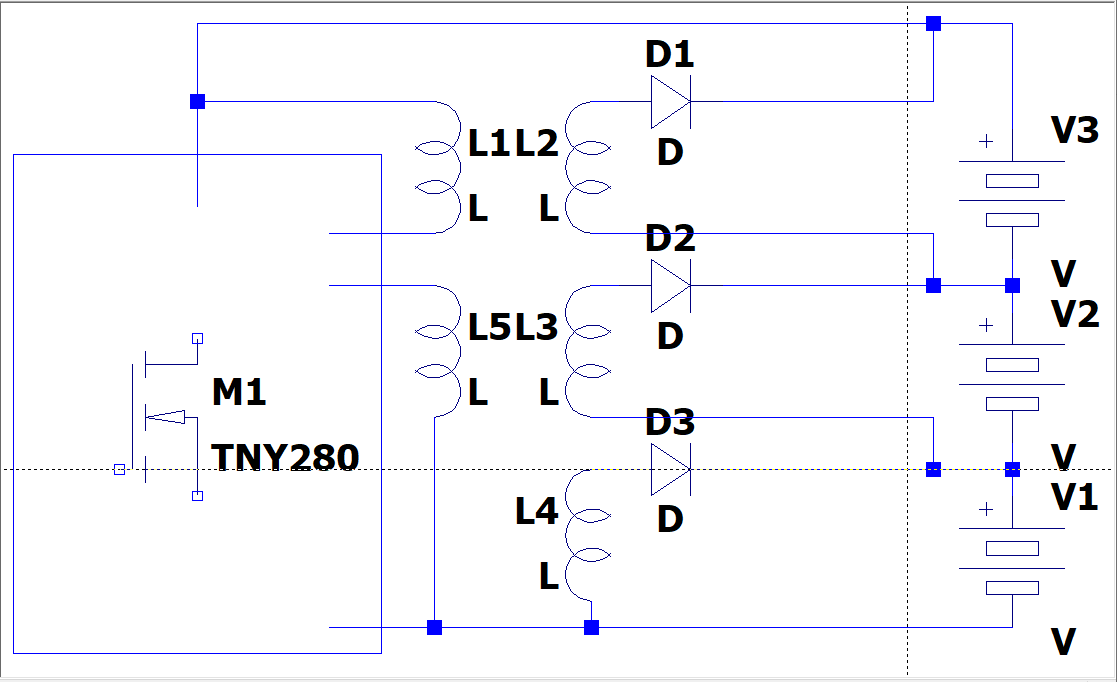

Ein Multi-Output Flyback, beim dem man Energie aus dem Gesamtpack entnimmt und in den Teilpack mit der geringsten Spannung einspeißt, dürfte grundsätzlich schon funktionieren.

Allerdings müßten die Ausgänge alle sehr symmetrisch aufgebaut werden, weil ansonsten die Probleme rund um das Thema "cross regulation" dafür sorgen, dass ein zu großer Teil der Energie auch in andere Teilpacks fließt.

Sobald die Teilpackspannungen auf wenige 100 mV angeglichen ist, dürfte die "Balancing-Effizienz" immer schlechter werden.

Die andere Variante, also mit einem eigenen Flyback aus jedem Teilpack in den Gesamtpack, ist wahrscheinlich unproblematischer im Handling.

Ja, im Übertrager müssen die Wicklungen bifilar sein. Für die relativ kleinen ausgangsspannungen pro 14/16s Pack eignet sich aktive gleichrichtung. Sicher nicht trivial, aber für den Ausgleich zwischen gleichartigen Packs braucht man nur wenig Leistung umzuschaufeln. Aufn ETD59 Kern kriegt man auch reichlich überdimensionierte Wicklungen drauf.

Ich überlege, ob das durchreichen von energie über den gesamten Stapel in normaler equalizer-Methode vielleicht schlechter ist, weil ja immer von einer Stufe zur nächsten wieder Verlust anfällt, also z.B. von Zelle 2 zu Zelle 30 der Ausgleich sowohl verlustbehaftet als auch schlechter ist. Die gleiche Ladungsmenge wird ja dann 56 mal umgespeichert.

Nur zur Info, ein JK BMS hat nur einen balancerkanal, der durch einen kompletten beidseitigen multiplexer aus jeder Zelle entnehmen, und in jede Zelle hineinschieben kann.

OK das ist schon viel besser als die dinger, die ich bisher in der Hand hatte. Bei diesem Stapel wäre das aber immer noch 8x Ladung schaufeln bei 4 packs. Ist der Ausgleich dann noch gut genug?

Nach meinem Kenntnisstand ist der MUX wie hier aufgebaut:

Der Wandler ist aber anders und geht nicht in den Stack sondern per DCDC zunächst in einen SuperCap und nach Umschalten des MUX dann zurück in eine andere Zelle

Schlimmer: "quad-filar"

Ökonomisch dürfte so etwas nur als Planar-Trafo realistisch sein.

Das wäre dann aber eine wirklich große Kanone für einen winzigen Spatzen.

Über einen ETD59 jage ich > 2.5 kW "Ultraschallleistung" ( 20 kHz) drüber.

Bei einem klassischen Schaltnetzteil wären es wohl > 5kW.

Zu den Wandler Wirkungsgraden gibt es ein nettes pspice ähnliches Spielzeug namens Epowersim. Daran sieht man schön die Auswirkungen auf den Wirkungsgrad. Wo die Schwächen liegen und was zu verändern ist um im Betriebslunkt besser zu arbeiten. Ich kam zu dem optimierten Ergebnis daß die Frequenz und Wicklung anfangs soweit zu verändern ist daß sich die Verluste im Halbleiter und der Spule in etwa teilen. Vorgegeben sind Standard Schaltungen die nach belieben abzuändern sind. Allerdings Leiterbahnen als Spulen, da müsste man schon ziemlich tricksen um vernünftige Ergebnisse zu erreichen. Vor allem zeigt das sowohl sofort die Sparversion auf. Für unmöglich halte ich es nicht wenn der Kern in der Bibliothek wäre. Habe mich nur mit Ring und EDT Kernen rum gespielt.

ja. Damit ein Ausgleich "dumm" funktioniert, brauchst 4 pins pro Kanal bei aktiver Gleichrichtung + 4 pins für die eingangsleistung + viel Kupfer aufm Kern. Man kann den Ausgleich auch einzeln gesteuert bauen, dann hast viel mehr Technik und kleiner Kern reicht.

Da hatte ich vor einigen Tagen ja schon argumentiert, warum das so sein muss.

Den DCX, den ich gezeigt habe, hast du gesehen?

Ab etwa 500 kHz haben klassische Wicklungen bei Schaltnetzteilen Probleme mit planaren Wicklungen mitzuhalten.

Bei 500 kHz ist ~ 105 um Kupferdicke optimal, Bei > 1 MHz kommt man dann langsam in den Bereich, wo man mit Standard 35 um im Optimum liegt.

Bei klassichen Wicklungen kommt man in dem Breich auch mit HF-Litze nicht mehr wirklich weiter.

Zudem sind bei solchen Frequenzen und hohen Strömen auch die "Terminierungsverluste" erheblich. Man muss also mit den synchronen Gleichrichtern ( SSR-FETs ) so nah an das Wicklungende wie es irgendwie geht.

Wenn man dann weiter optimiert geht es mit Techniken wie "Matrix Transformatoren" weiter.

Das ist alles praktikabel/ ökonomisch nur mit ins PCB integrierten Wicklungen umsetzbar.

Mit zunehmender Verbreitung von SiC und insbesondere GaN Halbleitern wird man das auch in Consumer-Ware immer öfter sehen.

@tageloehner Ich habe so einen einfachen aktiv Balancer hier, nur bisher noch immer nicht getestet. Ich denke viel besser als 100 mV Gleichlauf kann er nicht. Dafür aber für viele Zellen einfach erweiterbar.

Wobei meine kleinen NatriumIonen 3500mAh Zellen scheinbar sowieso selbst balancierend sind?

Starke Erwärmung gegen 4 V hin dafür mit vernichtendem Wirkungsgrad.

So schlecht daß ich mir nicht mal die Aufzeichnung ansehe. Muß die Ladespannung auf Kosten der Kapazität mal weiter auf 3,75V oder gar 3,70V absenken. Ladespannung angeblich 4,10V. vermutlich -5mV/°K?

SG

@nimbus4 "Innerhalb der Halbleiter entfallen dann grob 50% auf ohmsche Leitungsverluste und 50 % auf Schaltverluste. "

Genau auf das hin habe ich mit dem erwähnten Programm die Optimierung versucht. Irgenwie sollte es sogar selbst optimieren können. Oder bei Kupfer und Eisen Verlusten das gleiche Spiel. Ich setzte dann auch mal unmögliche 32 fach parallel handgewickelte Ringkerne mit besonderen Werkstoffen absolut voll gewickelt ein ![]()

Zum erwähnten Schaltnetzteil. Ja,sah ich.

Ich komme zwar ursprünglich aus der Leiterplattenfertigung, erste dicke Multilayer, daher vieleicht etwas blind. Es sollte mich niemand hindern Isolierschichten im 1/100 Bereich zu drucken. Damit komm dann allein schon der Kupfer Füllfaktor recht gut hin.

SG

Hallo,

geladen habe ich die Zelle mit 5 A. Entladen habe ich sie mit 10 A.

Die mitgelieferten Kabel mit den netten Krokoklemmen habe ich als Erstes gegen eigene mit gekrimpten Kabelschuhen gewechselt. Der Spannungsabfall ist sonst über die Krokoklemmen viel zu hoch. Da wird jede Messung ungenau.

Grüße

Thomas

@hopfen Ja. Gegen die Na-Zellen spricht bei mir 1. der noch hohe Preis, 2. die Verluste welche bei größeren Strömen noch fast bei meinen Bleiankern sind, und 3. der Spannungshub. Auch wenn alle meine Gerätschaften auf wenigtens 20-36V ausgelegt sind, ich will das nicht komplett ausreizen. Ich brauche aber notwendig eine Technologie, welche nach AT-Regeln sicher nicht brandgefährlich ist, dann kann ich mir nen Speicher ins Haus stellen. Bis dahin stellt sich der Vermieter quer.

Bei höheren Spannungen ( zig 100 V ), hohen Frequenzen und insbesondere wenn man "reinforced insulation" braucht, wird man praktisch bei einem PCB-Trafo, kaum unter 100 µm Isolationstärke kommen, eher merklich darüber.

Das ist bei hohen Frequenzen aber auch nicht wirklich kritisch.

Bei den flachen planaren Ferritkernen, würde man durch das Reduzieren der PCB-Dicke um ein paar 100 µm kaum Ferrit-Kernvolumen einsparen.

Auch wegen der sowieso schon prinzipiell hohen Kopplungskapazität bei PCB Wicklungen möchte man insbesondere Lagen unterschiedlicher Wicklungen nicht unnötig nahe aneinander bringen.

Wegen "proximity effect" kann man zudem Lagen einer Wicklung nur begrenzt direkt stapeln.

Interleaven auf einem einfachen Kern treibt die Kapazitäten nur weiter hoch und man bekommt die Verlustleistung der inneren Lagen immer schlechter weg.

Wenn man bei einem DCX ( mit nennenswertem Übersetzungverhältnis ) nach 99% Wirkungsgrad strebt dürfte sowieso kaum ein Weg an Matrix-Transformatoren vorbei führen, also eine Zerlegung in Teiltransformatoren, die auf einem speziellen Kern mit mehreren "center legs" in der Fläche realisiert werden. Ein solches Design hat eher unter 10 Kupferlagen.

Der gezeigte DCX hat insgesamt 12 Kupferlagen 105 µm und somit einen CU-Füllfaktor < 20%.

Bei planaren PCB Trafos im >> 100 kHz Bereich ist der Cu-Füllfaktor wegen der ganzen HF-Effekte nicht mehr der entscheidene Faktor.

Ganz im Gegenteil, wenn man meint mit "zu" dicken Kupferlagen, etwas Gutes zu tun, wird einem der "proximity Effect" dass mit massiv ansteigenden HF-Verlusten in der Wicklung quittieren.

OK, das erklärt dann die erstaunlich gute Effizienz von fast 97%.

Im Vergleich zu den ~ 99% die ein LFP Akku bei ähnlichen C-Raten schaffen dürfte, ist dass dann eher bescheiden.

Und bei den Strömen die in einer typischen ESS-Anwendung auftreten ( zumindest bei einem 48V LV System ), dürfte ein realistischer Zellwirkungsgrad dann wohl unter 95% liegen.

Das ist zwar nicht fatal aber auch nicht berauschend.

Hast Du schon irgendwelche Erfahrung zur Selbstentladung?

Warum nimmst du nicht das diy bms 4.9 von Stuart pittaway?